| Date       |  |

|------------|--|

| Date       |  |

|            |  |

| Instructor |  |

# Darlington and Cascode Amplifier Circuits

# **OBJECTIVE**

To calculate and measure DC and AC voltages in Darlington and cascode connection circuits.

# EQUIPMENT REQUIRED

# Instruments

Oscilloscope

$\mathbf{D}\mathbf{M}\mathbf{M}$

Function generator

DC supply

# Components

### Resistors

- (1)  $100-\Omega$

- (1) 51- $\Omega$ , 1-W

- (1)  $1-k\Omega$

- $(1) 1.8-k\Omega$

- (1) 4.7-k $\Omega$

- $(1) 5.6-k\Omega$

- $(1) 6.8-k\Omega$

- (1)  $50-k\Omega$  pot

- $(1) 100-k\Omega$

# Capacitors

- (1)  $0.001-\mu F$

- (4)  $10-\mu F$

### **Transistors**

- (2) 2N3904, (or equivalent general purpose npn)

- (1) TIP120 (npn Darlington)

### **EQUIPMENT ISSUED**

| Item               | Laboratory serial no. |  |  |  |  |

|--------------------|-----------------------|--|--|--|--|

| DC power supply    |                       |  |  |  |  |

| Function generator |                       |  |  |  |  |

| Oscilloscope       |                       |  |  |  |  |

| DMM                |                       |  |  |  |  |

|                    | <u> </u>              |  |  |  |  |

# RÉSUMÉ OF THEORY

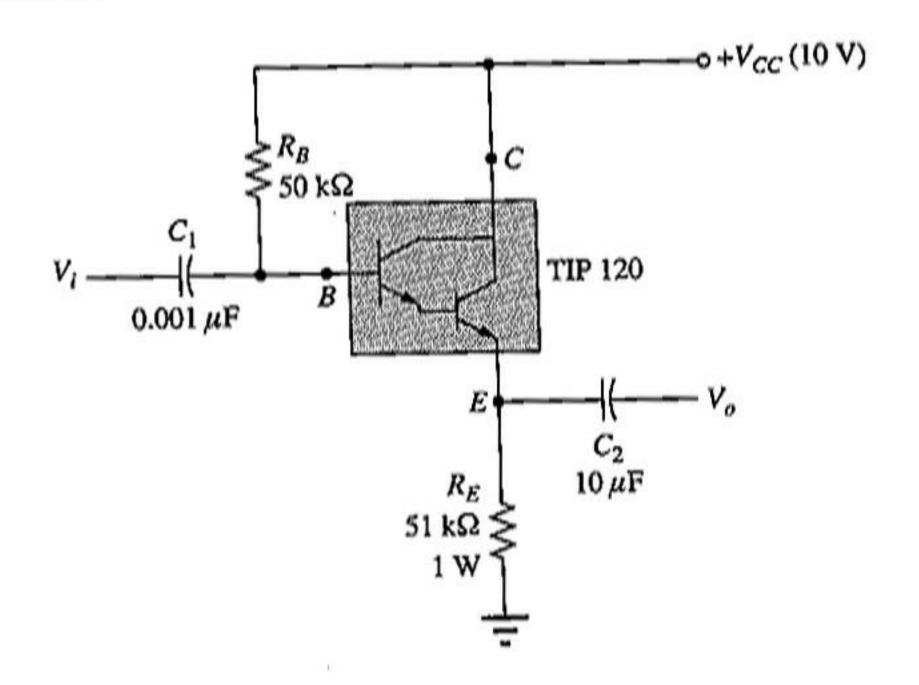

Darlington Circuit: A Darlington connection (as shown in Fig. 23.1) provides a pair of BJT transistors in a single IC package with effective beta ( $\beta_D$ ) equal to the product of the individual transistor betas.

$$\beta_D = \beta_1 \beta_2 \tag{23.1}$$

The Darlington emitter-follower has a higher input impedance than that of an emitter-follower. The Darlington emitter-follower input impedance is

$$Z_i = R_B \mid |(\beta_D R_E)$$

(23.2)

The output impedance of the Darlington emitter-follower is

$$Z_o = r_e \tag{23.3}$$

The voltage gain of a Darlington emitter-follower circuit is

$$A_v = \frac{R_E}{(R_E + r_e)} \tag{23.4}$$

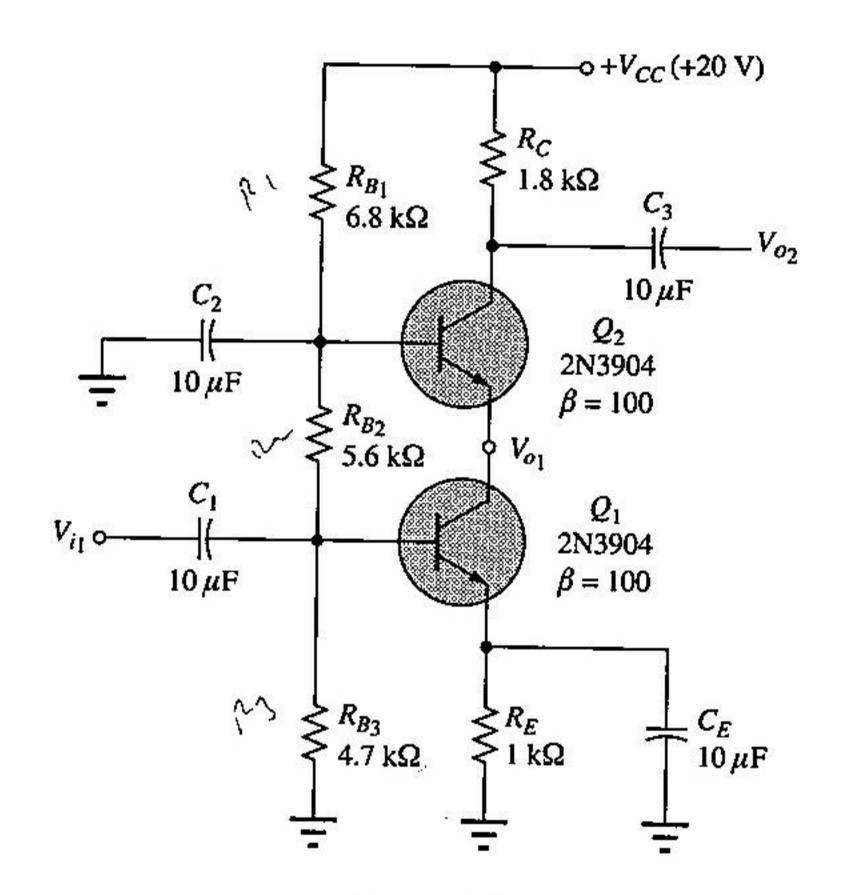

Cascode Circuit: A cascode circuit, as shown in Fig. 23.2, provides a common-emitter amplifier using  $Q_1$  directly connected to a common-base amplifier using  $Q_2$ . The voltage gain of stage  $Q_1$  is approximately 1, with the voltage  $V_{o1}$  being opposite in polarity to that applied as  $V_i$ .

$$A_{v_1} = -1 (23.5)$$

The voltage gain of stage  $Q_2$  is noninverted and of magnitude

$$A_{v_2} = \frac{R_C}{r_{e_0}}$$

(23.6)

resulting in an overall gain

$$A_v = A_{v_1} A_{v_2} = -\frac{R_C}{r_{e_2}} \tag{23.7}$$

# **PROCEDURE**

# Part 1. Darlington Emitter-Follower Circuit

a. For the circuit of Fig. 23.1 calculate the DC bias voltages and currents.

Figure 23-1

| $V_B$ | (calculated) | = |  |

|-------|--------------|---|--|

| $V_E$ | (calculated) | = |  |

Calculate the theoretical values of voltage gain, input and output impedance.

$$A_V$$

(calculated) =  $Z_i$  (calculated) =  $Z_o$  (calculated) =

b. Construct the Darlington circuit of Fig. 23.1. Adjust the  $50-k\Omega$  potentiometer  $(R_B)$  to provide an emitter voltage,  $V_E=5$  V. Using a DMM, measure and record the DC bias values:

| $V_B$ | (measured) | = |  |

|-------|------------|---|--|

| $V_E$ | (measured) | = |  |

$Z_o$  (calculated) =

| Calculate the base and emitter DC currents:                                                                                                                                                                                                                                                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $I_{B} 	ext{ (calculated)} =                                   $                                                                                                                                                                                                                                                   |

| $\beta_D  (\text{calculated}) = \\ \\ \textbf{c.}  \text{Apply an input signal } V_{\text{sig}} = 1  \text{V, peak at } f = 10  \text{kHz. Using the oscilloscope observe and record the output voltage to assure that the signal is not clipped or distorted. (Reduce the input signal amplitude if necessary.)}$ |

| $V_i  ({\rm measured}) = \underbrace{ \\ V_o  ({\rm measured}) = } $ Calculate and record the AC voltage gain:                                                                                                                                                                                                     |

| $A_v = V_o/V_i = \_\_\_$ art 2. Darlington input and Output impedance $ {\bf a.}  {\bf Calculate \ the \ input \ impedance:} $                                                                                                                                                                                     |

| $Z_i$ (calculated) =                                                                                                                                                                                                                                                                                               |

b. Connect a measurement resistor,  $R_x=100~{\rm k}\Omega$ , in series with  $V_{\rm sig}$ . Measure and record input voltage,  $V_i$ .

$V_i$  (measured) =

Calculate the circuit input impedance using

$$Z_i = \frac{V_i}{V_{\text{sig}} + V_i} R_x$$

$Z_i$  (calculated) =

Remove measurement resistor,  $R_x$ .

c. Measure the output voltage,  $V_o$  with no load connected.

$V_o$  (measured) =

Connect load resistor,  $R_L=100~\Omega.$  Measure and record resulting output voltage:

$V_o$  (measured) =  $V_L$  = \_\_\_\_\_

Calculate the output impedance using

$$Z_o = \frac{V_o - V_L}{V_L} R_L$$

$Z_o$  (calculated) =

Compare the calculated and measured values of  $Z_{\rm i}$  and  $Z_{\rm o}$ .

# Part 3. Cascode Amplifier

a. Calculate DC bias voltages and currents in the cascode amplifier of Fig. 23.2 (assuming base currents are much less than the voltage divider current).

Figure 23-2

| $V_B$ | (calculated) = |                    |

|-------|----------------|--------------------|

|       | (calculated) = |                    |

|       | (calculated) = | <del>0 103</del> 0 |

|       | (calculated) = |                    |

|       | (calculated) = |                    |

|       | (calculated) = | _                  |

| Cal   | 011 | ata | the | DC | hias | emitter   | currents      |

|-------|-----|-----|-----|----|------|-----------|---------------|

| C Par | CU  | ate | rme | -  | DIAG | CITITOUCT | CITY T CITYOR |

|                                                  | $I_{E_1}$ (calculated) =                                                                                                                                                                          |

|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Calculate the transistor dyna                    |                                                                                                                                                                                                   |

| b. Connect the cascode circuit of bias voltages. | $r_{e_1}$ (calculated) = $r_{e_2}$ (calculated) = $r_{e_2}$ of Fig. 23.2. Measure and record DC                                                                                                   |

| Calculate the values of emitter                  | $V_{B_1}$ (measured) = $V_{E_1}$ (measured) = $V_{C_1}$ (measured) = $V_{B_2}$ (measured) = $V_{E_2}$ (measured) = $V_{C_2}$ (measured) = $V_{C_2}$ (measured) = $V_{C_2}$ (measured) = $V_{C_2}$ |

| and the values of dynamic resis                  | $I_{E_1} = I_{E_2} = I_{E_3}$ stance:                                                                                                                                                             |

|                                                  | $r_{e_1} = $ $r_{e_2} = $                                                                                                                                                                         |

| c. | Using Eqs. 23. transistor stage | ā and | 23.6 | calculate | $\mathbf{the}$ | AC | voltage | gain | of | each |

|----|---------------------------------|-------|------|-----------|----------------|----|---------|------|----|------|

|    |                                 | 58    |      |           |                |    |         |      |    |      |

d. Apply input signal,  $V_{\text{sig}} = 10 \text{ mV}$ , peak at f = 10 kHz. Using the oscilloscope observe the output waveform  $V_o$  to make sure that no signal distortion occurs. If the output is clipped or distorted reduce the input signal until the clipping or distortion disappears.

Using the DMM measure, record the AC signals.

$$V_i \, ({\rm measured}) = \\ V_{o_1} \, ({\rm measured}) = \\ V_{o_2} \, ({\rm measured}) = \\ {\rm Calculate \ the \ measured \ voltage \ gains:}}$$

$$A_{v_1} = V_{o_1}/V_i =$$

$$A_{v_2} = V_{o_2}/V_{o_1} =$$

$$A_{v} = V_{o_2}/V_i =$$

Compare the measured voltage gains with those calculated in steps  $3(\mathbf{c})$  and  $3(\mathbf{d})$ .

e. Using the oscilloscope, observe and record waveforms for the input signal,  $V_i$ , output of stage 1,  $V_{o_1}$ , and output of stage 2,  $V_{o_2}$ . Show amplitude and phase relations clearly.